:no_upscale():quality(80)/https%3A%2F%2Fimg.4gamers.com.tw%2Fckfinder%2Ffiles%2FElvis%2FNews%2F2021-05%2FIBM_Research_2_nm_Wafer.jpg%3FversionId%3DQlaDdFTUqwP2gCugxOAM8GdY2PK2udEy)

IBM 推出以「2nm」為名的製程工藝,並宣稱是世界首款 2nm 製程。然而因為每種工藝技術的定義不同,這款 2nm 可能不如想像中的厲害。

通常,當製程工藝尺寸縮減至下個數量級時,每單位晶圓面積的電晶體密度通常可成長 50%,進而讓晶片面積縮小。然而,當 FinFET 技術興起時,電晶體密度成長/晶片面積縮減幅度卻逐漸偏離製程工藝尺寸的真實數值。

事實上,當今沒有任何一家晶圓製造商使用真實的製程公尺寸數值來命名。如果按照電晶體密度嚴格審視,Intel 的製程工藝尺寸大概是台積電的兩倍。

舉例來說,Intel 7nm 製程的電晶體密度其實跟台積電 5nm 製程差不多,而台積電 5nm 製程的電晶體密度只比自家 7nm 製程成長 15% 而已。

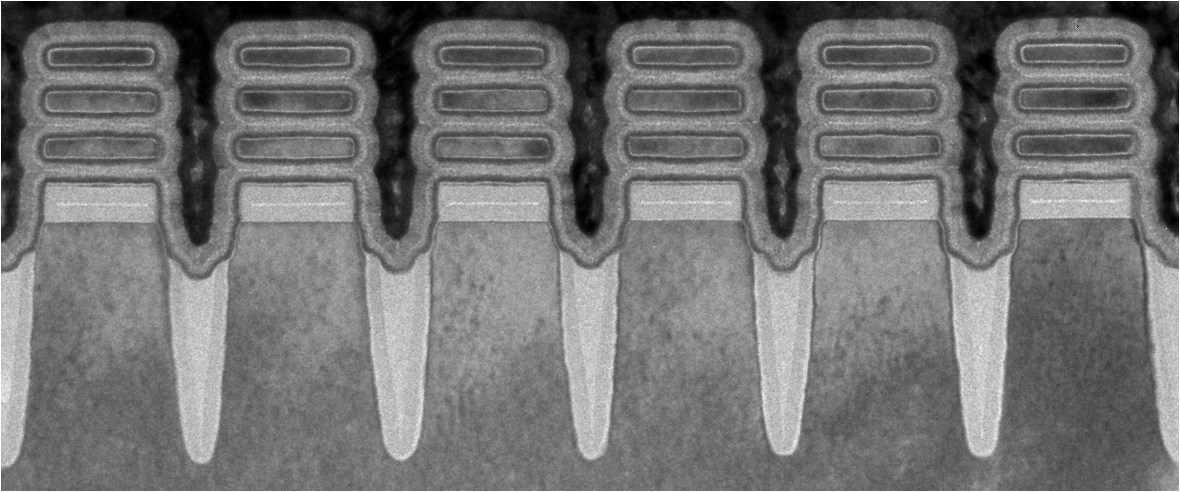

根據 IBM 的說法,他們的 2nm 製程使用的是 nanosheet(奈米片)技術,電晶體密度比台積電的 5nm 提高了 50%。這意味著,即便使用現今最寬鬆的標準,也只能稱作 3.5 nm 而已。

隨著光刻技術日新月異,尋找工藝尺寸繼續縮小的 FinFET 或其他製造技術的競賽仍在進行中。High-NA(高數值孔徑)EUV 就是其中之一,而 IBM 使用 nanosheet 則是另一種可行方式,這也許比單純縮小工藝尺寸來得更重要。