:no_upscale():quality(80)/https%3A%2F%2Fimg.4gamers.com.tw%2Fpuku-clone-version%2Ff820ee518bb2df4eb88083ebef650229851d60ea.jpeg)

AMD 下一代 Zen 6 處理器架構會採用台積電的 2 nm 製程,過去有一些猜測可能會利用更高製程,讓處理器獲得更多 CPU 核心,不過根據最新爆料指出,AMD 採用的小晶片封裝方案會維持長久以來的規格配置,每一顆 CCX 晶片上限會是 12 核,快取則是上升到 48 MB。

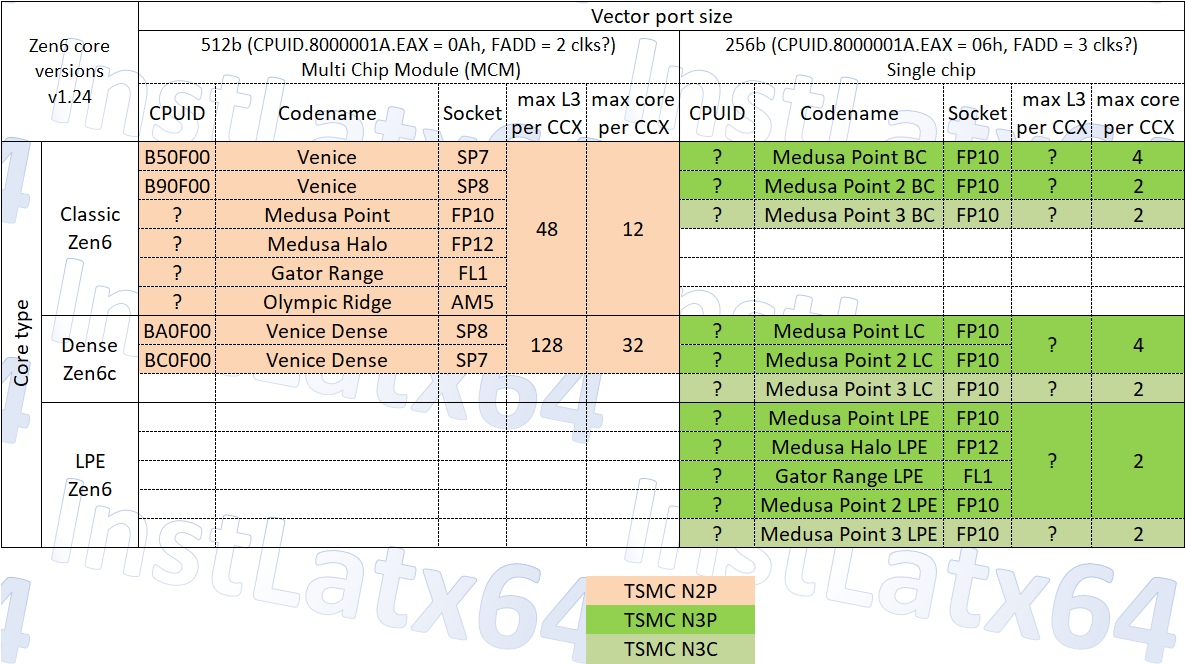

爆料者 @InstLatX64 透過從 AMD 更新支援後的核心程式碼中,推斷出 Zen 6 架構對應的 ID 編號為 B80F00,並根據代號整理出一系列對應產品,得知 Zen 6 將會有三種變體:Classic Zen 6、Dense Zen 6c、LPE Zen 6。

其中 Classic Zen 6 就是標準版的 Zen 6 架構,會用在開發代號為 Venice、Medusa Point、Medusa Halo、Gator Range 和 Olympic Range 上。而 Olympic Range 採用 AM5 腳位,代表是 PC 上的 Ryzen 處理器,Venice 為伺服器 EPYC 處理器,剩餘的則是筆電與行動處理器。

依照 AMD 的處理器設計,CPU 會封裝在 CCX 小晶片中,在 Zen 6 架構上,CCX 的核心密度沒有增加, 每一組保持在 12 核心,不過 L3 快取的容量從過去的 32 MB 加大到了 48 MB。

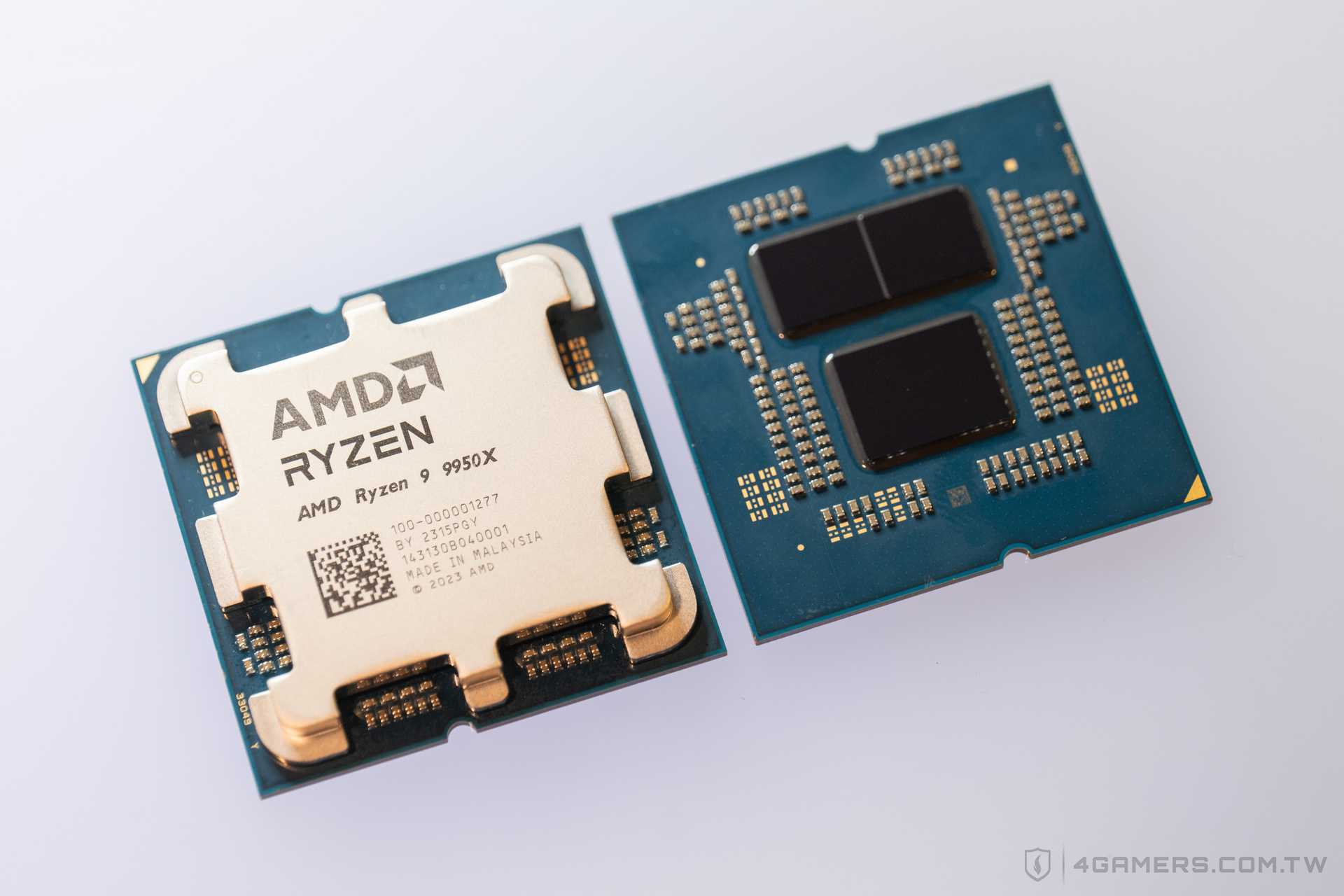

這意味著,倘若下一代消費 PC 上的 Ryzen 處理器還是由 2 顆 CCX 組成,最大的核心會是 24 核不變,但 L3 快取會從 Ryzen 9 5950X 以來的 64 MB 提升到 96 MB,單核性能不僅將能獲得進一步增長,也意味 X3D 版本就算維持追加 64 MB 快取,容量也會從現在的 128 MB 來到 160 MB。

除 Zen 6 之外,變體版本 Dense Zen 6c 會如同其名,擁有極高密度的核心與快取,單 CCX 的 CPU 數量達到 32 顆,L3 快取更來到 128 MB,但規劃上只會用在代號 Venice 的 EPYC 伺服器上。

傳聞其中一款會由 8 組 CCX 組成,實現高達 256 核、1024 MB(1 GB)的 L3 快取,與之對比目前最高階採 Zen 5c 架構的 EPYC 9965 也才 192 核、384 MB L3 快取。

最後,LPE Zen 6 推測應該是所謂的低公耗版本,預計是給入門行動或嵌入式裝置,製程會降為台積電的 3 nm,CCX 內的 CPU 數量最多也只有 4 顆,快取容量尚未知曉。

關於 Zen 6 架構的詳細改變還不完整,但從本次爆料,可以看出 AMD 在規劃上持續注重利用快取加大來強化單核心的性能,多核心競爭則改投入到 Zen 6c 由工業級的 EPYC 處理器承擔上,讓帳面規格上,Zen 6c 超高密度的配置要比 Zen 6 明顯大膽許多。